Electrostatic discharge (ESD) is a major threat for integrated circuits reliability. ESD failures can occur during manufacturing, assembly, shipment or in the field. Charged objects discharge through the IC pins with very high currents with a short discharge duration, which can cause irreversible damage. On-chip protection devices that can shunt high currents and clamp voltages within safety margins must be designed with minimized size and capacitive loading of the core circuitry to protect chips against ESD, and at the same time they must not disturb normal operation [1].

Physics-based technology computer aided design (TCAD) numerical simulation of the device fabrication process and of the device electro-thermal behavior can identify and investigate ESD relevant effects and the internal operation of the device under ESD stress condition, which are not generally accessible by measurement. For instance, it can be successfully used for the study of 3D effects arising from device layout and/or inhomogeneous current (Figure 1). Nevertheless, treating ESD-related problems by means of TCAD is also a very challenging task in terms of device modeling [2, 3]. The main challenge consists in fast transients, high currents, and temperature-dependent modeling at the limit of the model’s validity. Simulator model’s calibration to the high temperature and high current regime is therefore of central importance.

In the context of technology on-chip ESD protection development, TCAD tools can help design, analyze, and optimize the performance of ESD protection devices and troubleshoot ESD issues to save time and money during technology development, both on single device level and on circuit level by using dedicated, physics-based ESD circuit compact models derived from TCAD. This methodology – spanning from TCAD to SPICE – allows checking critical I/O protection configurations before IC tape-out and avoiding re-designs.

Introduction

The operational regime of devices under ESD stress is far outside the range of normal operation conditions. Among the most important effects to be considered in the ESD regime are self-heating, conductivity modulation due to high carrier injection, non-uniform operation (current filamentation) [4, 5], and avalanche breakdown at reverse-biased junctions. As already mentioned, for investigating these effects, TCAD process and device simulation represents a valuable tool, which often can replace or at least can complement expensive measurements.

The characterization by means of transmission line pulsing (TLP) measurements allows the extraction of ESD parameters under controlled, quasi-static conditions, providing an essential tool for debugging of ESD issues [6]. So-called 100ns-TLP and very-fast (vf-)TLP is used to perform calibration of high-current, high-temperature regime characteristics to measurements for different relevant time domains. For verification of ESD robustness in TCAD, the standard qualification models such as the Human Body Model (HBM) in the 100ns time domain and the much faster and harsher Charged Device Model (CDM) in the 1-2ns time domain are used [7]. A tight correlation in terms of failure signature and failure current level/robustness exists between 100ns-TLP and HBM (failure mostly due to thermal overload), and between vf-TLP and CDM (failure mostly due to voltage peaks leading to gate oxides breakdown).

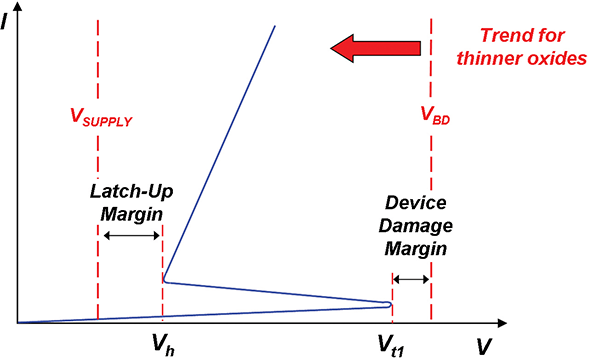

The basic functionality of an ESD protection device or ESD protection circuit is given by providing a low resistivity discharge current path which prevents the internal circuitry as well as the protection device/circuit itself from being damaged during an ESD event, and is “transparent” to the internal circuitry under normal operation conditions. Some of the actual challenges for ESD protection are represented by the shrinking gate oxide of core devices which result in a reduction in breakdown voltage, by the increase of capacitive load due to large area protection devices which limit I/O speed and deteriorate performance of RF circuits, and by the increased complexity of clamping circuits design due to multiple supply voltages and latch-up immunity requirements. Figure 2 shows the most important parameters of the so-called ESD design window for ESD protection devices.

TCAD ESD Workbench

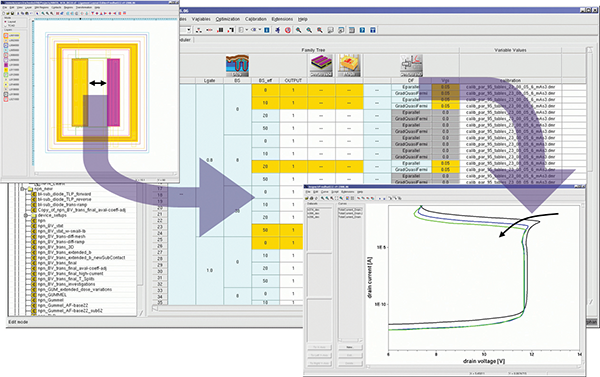

Establishing a full-fledged ESD TCAD Workbench from process and layout information, and calibration of simulation models including high-current/high-temperature regime targeted to device engineers and TCAD teams allows the evaluation of process variation influences, determination of layout dependence, and optimization of ESD structures (Figure 3) [8]. The improved understanding of device internal failure modes allows developing better I/O protection structures and the possibility for virtual testing and development of new structures. TCAD speeds up the ESD design to keep pace with IC development at reduced design-cycles times by reducing time-to-market and cost-to-market.

It is important to select the right models that can capture the complicated effects described above during the operation of the ESD protection device. The drift-diffusion model is sufficient to characterize transport during ESD operation. The starting point for a successful calibration of a device’s ESD characteristics is represented by a well calibrated normal operation regime process and device simulation model set in 1D with using SIMS data, and 2D with using TEM/SEM, CV, and electrical point data for e.g., VTH and DIBL, possibly with including substrate bias effect. In a further step, ESD effects related modeling and calibration (Figure 4) [9] is performed with considering:

- High-temperature calibrated models

- Impact ionization

- Band-to-band tunneling

- Mobility (low-field, carrier-to-carrier-scattering, high-field-saturation)

- Bipolar-specific models (snapback phenomenon)

- Band-gap narrowing

- SRH and Auger recombination

- Electro-thermal effects

- Self-heating mechanisms and heat flows

- Information about layout and measurement setup

- 3D layout features

- Contact resistances

Impact ionization must be turned on to capture breakdown and snapback effects. Band-to-band tunneling models may be required for gated devices, especially at steep pn junctions with high electric fields. Bandgap narrowing may also need to be included if there are regions with high doping concentration. Since the temperature of the device increases during ESD operation, temperature-dependent Shockley-Read-Hall and Auger recombination models may need to be included. Mobility models that include carrier-carrier scattering both in the bulk and in the inversion/accumulation layers may be needed. Thermodynamic models that account for heat conduction and generation within the device are needed to capture self-heating. Finally, since most ESD devices are inherently 3D in nature, 3D simulations may be needed to accurately model inhomogeneous current flow [10].

At the end, the goal is to obtain one set of parameters which allows the predictive simulation of ESD behavior and at the same time can be used for normal operation conditions as well.

Layout Variations

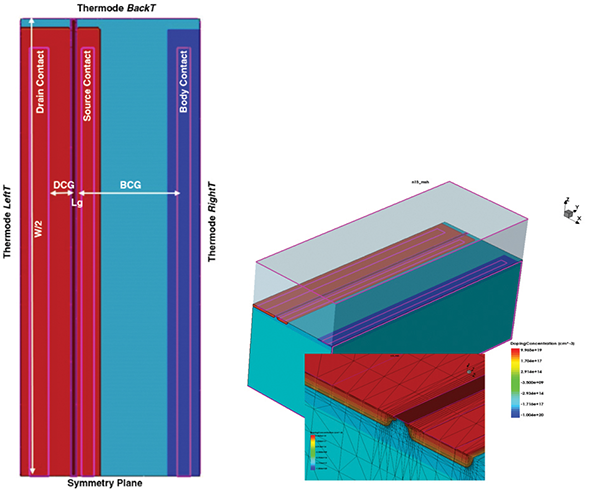

The most important aspect of ESD device design is layout optimization. Figure 5 shows the layout of a gate-grounded NMOS ESD protection device modeled by 3D TCAD (top view of the device with layout parameters and the electrical and thermal contacts).

Dimensions such as gate-length, drain-to-gate spacing, body-to-gate spacing and device width are important in optimizing the performance of the ESD device. In TCAD, these layout parameters are specified as variables, so that one can simulate and optimize these parameters in three-dimensions to obtain the desired/required ESD device performance.

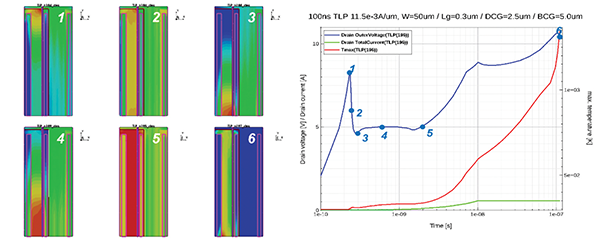

Inhomogeneous Operation

Another important characteristic of a well-designed ESD protection device is its ability to continuously withstand high stress in terms of current, voltage and temperature in as limited a silicon area as possible. This also reduces the capacitive load. One way to achieve that is to ensure that the device operates as homogeneously as possible. Three-dimensional TCAD simulations can help investigate the uniformity of operation under ESD stress.

Thermal Failure

The simulation of ESD failure is complex. In the case of thermal failure, one can distinguish two simple cases that can be easily simulated with TCAD.

One way is to monitor the maximum temperature occurring in the device during an ESD simulation. If the temperature exceeds the melting point of silicon or metal (if the temperature hot-spot occurs in the proximity of contacts), one can regard the device as having failed.

The second approach is to consider the occurrence of turning points in the I-V or V-t characteristics (negative differential resistance) as the onset of thermal runaway. Thus, TCAD can provide insight into the breakdown mechanism of the device, which can be hard to ascertain by other methods.

Example of Three-Dimensional TCAD Simulation

The 3D structure of Figure 5, with the appropriate mesh, is considered to perform 3D device simulations as shown in Figure 6. A 3D approach is essential to understand the non-uniform operation effects arising from device layout and/or high current and high temperature that occur under TLP and HBM/CDM model stress types, such as non-uniform triggering and failure due to thermal overload.

TCAD-Based Circuit Compact Models For ESD

There is a high need to include ESD compact models in circuit simulation for predicting critical current paths and critical (I,V) node values and enhance I/O design quality. The insight gained by TCAD allows developing physically based compact model add-ons for ESD. Internal device characteristics not accessible by measurements can be studied. Calibrated process and device simulation therefore allows physics based parameter extraction for ESD compact models while avoiding expensive, noisy and destructive measurements.

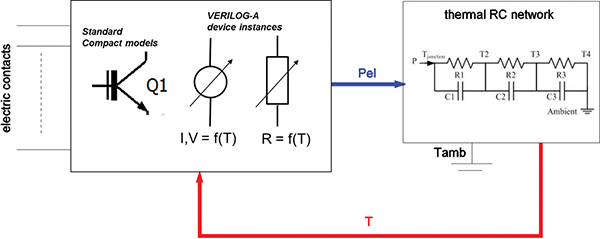

To keep the compact model development effort to a reasonable level, a modular modeling strategy is recommended. This strategy is often also referred to as “macro-modeling” or “sub-circuit modeling” in the literature. We retain the corresponding device’s standard model (e.g., a Gummel-Poon or BSIM model) for normal operation conditions and extend it by ESD-specific add-on modules to form a full ESD compact model. The operational regime of devices under ESD stress is far outside the range in which the standard compact models have been tested and verified, whereas the full ESD compact models allow reproducing behavior under ESD stress in circuit simulation. Thermal effects are included by establishing a feedback loop between electric and thermal domains. The thermal domain is modeled using first or higher order thermal RC-networks depending on the complexity of the device’s temperature fields (one or more highly localized hot spots or almost homogeneous distribution). Figure 7 shows schematically how the ESD compact models are set up.

A dedicated methodology for the automatized extraction of the custom ESD compact model parameters is developed based on the calibrated ESD TCAD workbench, as outlined in Figure 8.

The calibrated ESD compact models can be employed within circuit simulations to determine critical current paths, to identify endangered devices, and to optimize protection circuitry. Circuit simulations with up to 50 ESD protection devices and few 1000s standard devices are feasible. The limitation arises from the well-known convergence problems, caused by the strong nonlinear behavior of the protection devices under ESD stress conditions and from their interaction with the rest of the circuit. The nonlinearities cannot be eliminated but can be reduced to an acceptable level by paying attention to numerical issues. While the nonlinear behavior (e.g., snapback devices) is one of the key issues to account for in ESD simulations, it makes the numerical treatment extremely unstable and computing intensive. Nevertheless, the circuit complexity can go beyond simple I/O pad protection configurations, including also large parts of the internal circuitry. For the implementation of the ESD add-on model equations, VERILOG-A behavioral modeling language can be used. VERILOG-A can be read by the most common circuit simulators in use such as HSPICE®.

ESD Circuit Simulation Example

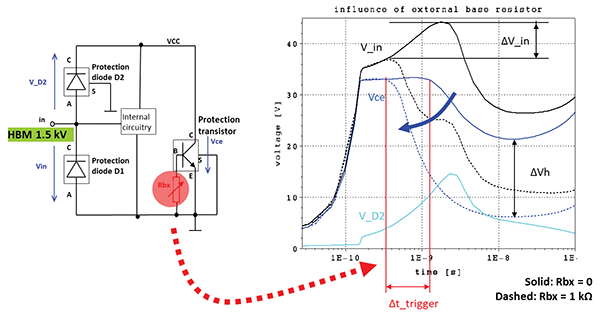

In Figure 9, the ESD compact models for a protection NPN transistor and for two protection diodes are used within an input pin protection HBM circuit simulation. For simplicity, the internal circuitry comprising the first stages of the circuit is sketched by a box only. The protection diode ESD compact models include effects such as voltage overshoot due to forward recovery [11], reverse breakdown, and conductivity modulation due to high-injection, and – in case of the high-side diode D2 – a parasitic PNP transistor towards the substrate. The NPN compact model accurately models the pre-avalanche breakdown/weak avalanche breakdown regime [12], which determines the snap-back triggering current level.

Applying positive HBM stress between the input pin and ground, leads to a main current flow through D2 and the protection NPN, which goes into snap-back and thus limits the voltage at the VCC line. The voltage at the input pin is given by the sum of the voltages at VCC and the voltage drop across D2. Due to the diode forward voltage overshoot, the voltage drop across D2 can exceed the stationary DC voltage drop by a considerable amount. The parasitic PNP action is not relevant under these stress bias conditions. It is shown, that the transient voltage peak at the input pin is reduced by increasing the triggering speed of the protection NPN by means of an external base resistance. The external base resistance decreases the amount of current needed to forward bias the base-emitter junction and therefore the snap-back occurs earlier.

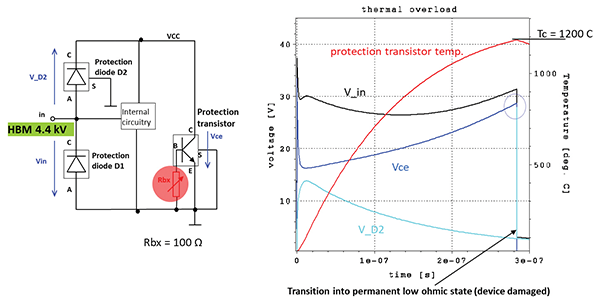

At the same time the holding voltage Vh is decreased to a value that could be potentially too low and lead to latch up issues (see Figure 2). Therefore, triggering speed needs to be traded off with sufficient holding voltage. If the HBM pre-charge voltage is increased from 2kV to 4.4kV, the protection NPN transistor is damaged by second breakdown. In the circuit simulation shown in Figure 10, this happens as soon as the protection NPN temperature has reached a pre-defined critical temperature Tc.

Summary

ESD is a real threat for integrated circuit reliability and therefore, meeting ESD robustness specifications is mandatory.

TCAD simulation is a very powerful tool to identify and investigate ESD-relevant effects and the device’s internal behavior under ESD stress conditions which are in general not accessible by measurement, such as for the study of 3D effects arising from device layout and/or inhomogeneous current. The outlined TCAD-based ESD compact modeling methodology opens for the possibility to investigate and optimize ESD protection circuits with dedicated, physics-based ESD compact models that allow us to take self-heating, layout, and process related effects into account at circuit level.

The value of TCAD for ESD can be summarized by the reduction of IC and device design-cycles time, and eventually by making “first silicon success” possible, ensuring competitiveness of products on the market.

References

- ESD Association https://www.esda.org/esd-overview/esd-fundamentals/

- M. P. J. Mergens, On-Chip ESD Protection in Integrated Circuits: Device, Physics, Modeling, Circuit Simulation, ETH Dissertation no. 14185, Hartung-Gorre Verlag Konstanz, 2001.

- K. Esmark, H. Gossner, W. Stadler, Advanced Simulation Methods for ESD Protection Development, Elsevier Oxford, 1st ed., 2003.

- Ch. Russ et al., “Non-uniform triggering of gg-nMOSt investigated by combined Emission Microscopy and Transmission Line Pulsing”, EOS/ESD Symposium, pp.177–186, 1998.

- D. Pogany et al., “Quantitative Internal Thermal Energy Mapping of Semiconductor Devices Under Short Current Stress Using Backside Laser Interferometry,” IEEE Transactions on Electron Devices, vol. 49, no.11, pp. 2070–2079, 2002.

- J. E. Barth et al., “TLP Calibration, Correlation, Standards, and New Techniques”, IEEE Transactions on Electronics Packaging Manufacturing, vol. 24, no. 2, pp.99–108, April 2001.

- ESD Association https://www.esda.org/esd-overview/esd-fundamentals/part-5-device-sensitivity-and-testing/

- SentaurusTM TCAD user guide, version P-2019.03, Synopsys, Inc. 2019

- T. Cilento et al., “Simulation of ESD protection devices in an advanced CMOS technology using a TCAD workbench based on an ESD calibration methodology”, Microelectronics Reliability 50 (2010), pp. 1367-1372

- T. Cilento et al., “Investigation of layout effects in diode-triggered SCRs under very-fast TLP stress through full-size, calibrated 3D TCAD simulation”, Microelectronics Reliability 88-90 (2018), pp. 1103-1107

- K. J. Tseng, “Modeling of diode forward recovery characteristics using a modified charge-control equation”, International Journal of Electronics, vol. 84, no. 5, pp. 437–444, 1998.

- S. L. Miller, “Ionization rates for holes and electrons in Silicon”, Phys. Rev., vol. 105, no. 4, pp. 1246-1249, 1957