Part 1: Top-Level Description of the Design Problem

This is the first of three articles devoted to the design, test, and Electromagnetic Compatibility (EMC) immunity evaluation of multilayer PCBs containing analog circuitry. In this study, there are seven design variants that all contain a similar schematic but implement different PCB layout techniques.

All variants were equipped with an analog voltage measurement along with a temperature measurement [1]. Non-conductive and metallic enclosures were evaluated for cases where the design options showed susceptibility issues. Testing was performed according to the ISO11452-11 Radiated Immunity Reverberation Method standard from 200MHz – 1GHz up to 100V/m and ISO11452-4 Bulk Current Injection from 1MHz – 400MHz up to severity level 4. The analog readings were monitored during RF immunity testing to determine the performance of the various design options.

In this introductory article, we present a top-level block diagram description of the design problem under research. The subsequent articles will be devoted to the RF immunity performance of the PCB assemblies.

1. Introduction

Electronic products that are sold in the marketplace must undergo a series of EMC tests to demonstrate compliance with industry and regulatory requirements. One aspect of the requirements focuses on evaluating a device’s conducted and radiated immunity performance. This evaluation begins with developing a prototype design (schematic and PCB layout), then follows with EMC testing a functional part early in the design process. Early test results typically lead to design changes and an understanding of what is required to become compliant. The objective of this study is to provide guidelines for schematic and layout design concerning EMC immunity of analog circuitry.

Many electronic devices use sensors to monitor their environment, interpreting analog signals and quantizing them into discrete values for digital use. For example, temperature and battery voltage are commonly measured in a variety of applications, which is the case in this study.

2. Top-Level Block Diagram

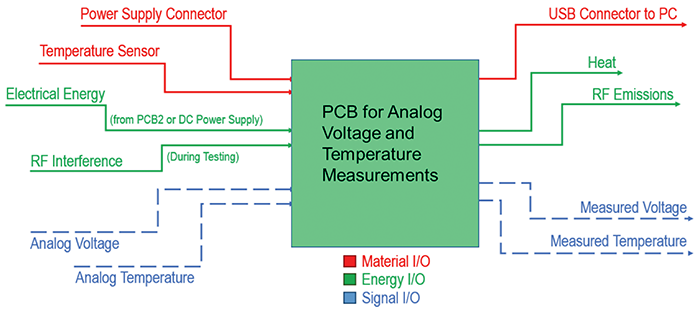

The PCB inputs and outputs are shown in Figure 1.

There are three macro inputs to the system which include physical connections (materials), energy (power supply & RF exposure), and signals representing the environment (voltage & temperature). Outputs from the system are the USB connector (electrical RX/TX signals being monitored), heat energy, and unintentional RF emissions. While there are some low-level RF emissions radiating and conducting from the evaluation boards, these will not be considered in this study.

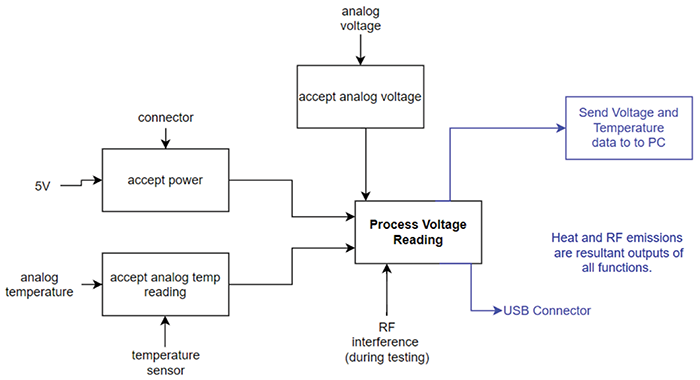

For the purposes of this study, we focused on the electrical interfaces. A 5VDC supply was provided to power the PCB. A separate 12VDC power supply was provided for the analog voltage measurement. Additionally, a thermocouple was connected to the analog measurement port. In response, the PCB provided the measured values of Voltage & Temperature over UART back to the PC through a fiber optic interface. The functional structure of the measurements is shown in Figure 2.

3. PCB Variants

PCB routing design can have a significant effect on analog RF immunity performance. In this study, we evaluated design options such as routing the analog lines as microstrip and stripline configurations. Additionally, the analog traces were routed as single-ended or as a differential pair. Finally, some of the variants utilized either a single PCB ground or a split analog/digital ground. A summary of the various routing implementations is shown in Table 1.

| Variant | Analog Trace Routing Style | Analog Trace Routing Layer | Grounding Method | Ground Split Geometry | Ground Split Layers |

| 1 | Differential | Microstrip on top layer | Single Ground Reference (GND) | N/A | N/A |

| 2 | Single Ended | ||||

| 3 | Differential | Embedded on layer 3 | |||

| 4 | Single Ended | ||||

| 5 | Single Ended | Microstrip on top layer | Split Ground Reference (AGND and GND) | AGND under analog circuitry, adjacent to GND* | All layers |

| 6 | AGND under analog traces, surrounded by GND* | Layer 2 only | |||

| 7 | 1-3-1-3-1-3-1-3-1 |

Table 1: Routing Implementations

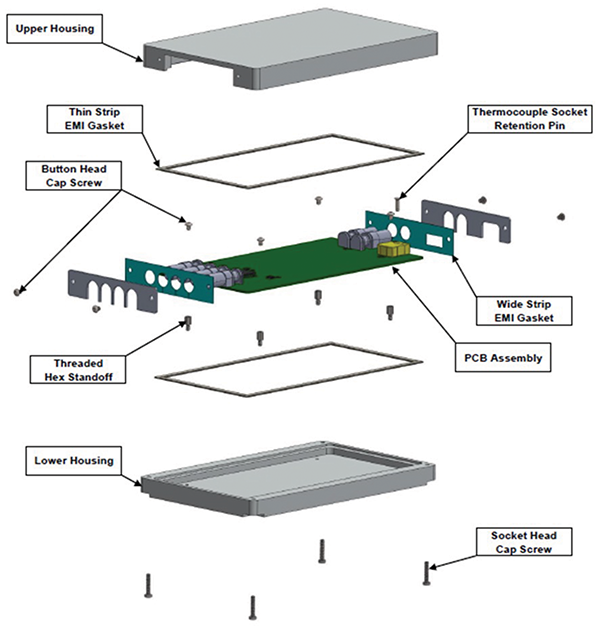

Seven variants were designed, fabricated, and tested to understand the benefits of these various design techniques. The test results led to the identification of good design practices for similar circuits in a wide variety of industries. All variants of a given board family were designed to be tested using one of two custom-built PCB enclosures. The first enclosure, which is conductive (shown in Figure 3), was machined from 6061 aluminum and uses threaded fasteners for closure.

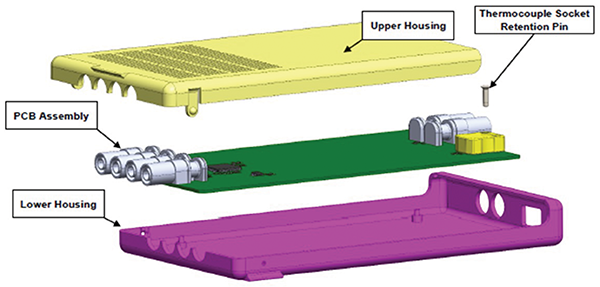

The second, non-conductive enclosure (shown in Figure 4), was 3D printed using nylon and uses snap hook and lip groove features for closure.

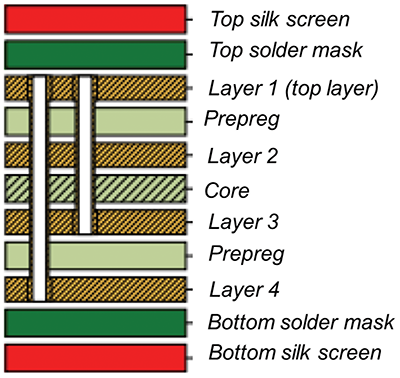

All seven variants used the same PCB stack up, shown in Figure 5.

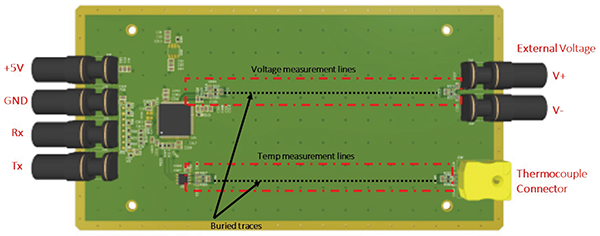

Figure 6 shows the PCB with analog traces on the top layer. This configuration was used in variants 1, 2, 5, and 6.

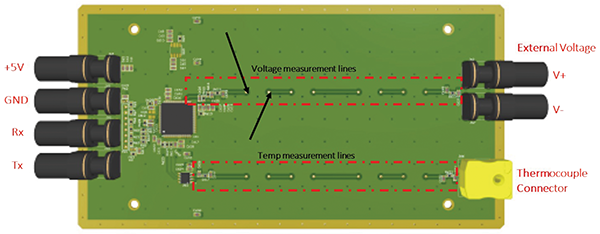

Figure 7 shows the PCB with the analog traces buried on layer 3. This configuration was used in variants 3 and 4.

Figure 8 shows variant 7 PCB with the traces jumping between the top layer and layer 3.

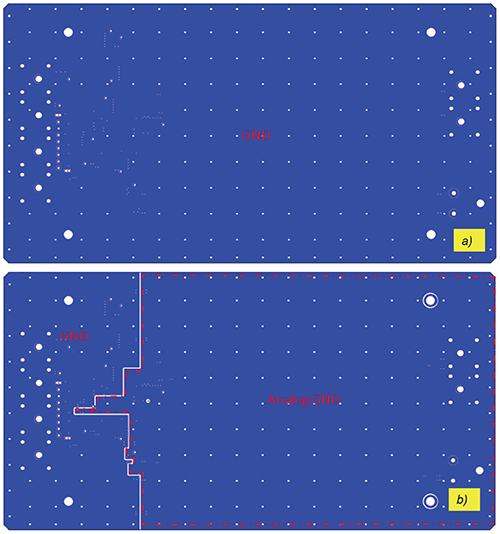

Variants 1, 2, 3, and 4 used a solid ground plane on layer 2 (shown in Figure 9a), while variants 5, 6, and 7 used a split ground plane (shown in Figure 9b).

4. Immunity Testing Plan

After validating the functionality of all PCB assemblies, radiated immunity (ISO11452-11) and conducted immunity (ISO11452-4) testing were performed within the frequency range of 200MHz to 1GHz. The test configurations shown in Table 2 represent component placement and enclosure type used during testing to evaluate EMC performance for each design.

| Test Descriptions | ||

| Configuration A | Configuration B | Configuration C |

| No filters on measurement signal traces, non‑conductive enclosure | No filters on measurement signal traces, conductive enclosure, (4) non-conductive standoffs, no conductive ground ring gaskets | Selective filtering on measurement signal traces, conductive enclosure, (4) conductive standoffs, conductive ground ring gaskets (top and bottom) |

Table 2: Description of test configurations

Configuration A utilized a non-metallic enclosure. Configuration B utilized a conductive enclosure with non-conductive standoffs to isolate the enclosure from the ground. Configuration C utilized a conductive enclosure with conductive standoffs and two conductive gaskets to improve upper and lower housing bond to the PCB GND. Additionally, selective filtering components were utilized on the analog traces to improve RF immunity.

All seven variants were tested using Configuration A. The three variants which exhibited the weakest RF immunity performance were re-tested in the frequency bands where the failures occurred, using Configuration B (variants 1,5,6). Finally, the worst performing variant from the second round of testing (Configuration B) was re-tested using Configuration C (variant 1), again in the frequency bands where the failures occurred.

5. Future Work

The next article will discuss radiated immunity testing and results.

References

Baatar, B., Costantino, C., Morey, R., Muldowney, C.,

“EMC PCB Design Study”, GVSU senior project sponsored by E3 Compliance, LLC.